# HDL-МОДЕЛЬ ПАМЯТИ RAM CO ВСТРОЕННОЙ СХЕМОЙ ГЕНЕРАЦИИ НЕРАЗРУШАЮЩИХ ТЕСТОВ

Малиновский М. Л.<sup>1</sup>, Аленин Д. А.<sup>2</sup>, Барсов В. И.<sup>2</sup>, Сидоренко А. В.<sup>3</sup>

<sup>1</sup> Харьковский национальный технический университет сельского хозяйства имені П. Василенко, <sup>2</sup> Украинская инженерно-педагогическая академия (г. Харьков), <sup>3</sup> Научно-производственное предприятие "Стальэнерго" (г. Харьков)

Предложена HDL-модель памяти RAM со встроенной схемой генерации неразрушающих тестов, которая позволяет повысить эффективность проектирования цифровых систем для ответственных приложений.

Постановка проблемы. Проблеме создания цифровых систем на основе микросхем программируемой логики (FPGA) посвящено множество исследований. Интерес к FPGA обусловлен быстро развивающимися технологиями их производства и значительным расширением области их применения, в частности в системах, связанных с безопасностью. В то же время, увеличение сложности систем на кристалле сопряжено с введением рисков и повышением вероятности ошибок на этапе проектирования.

Одним из широко распространенных подходов к повышению эффективности проектирования систем на основе FPGA является создание библиотек стандартных настраиваемых компонентов для различных предметных областей. Если разрабатываемая система связана с безопасностью, то такие компоненты должны обладать некоторыми специфическими свойствами. Например, они могут быть резервируемыми и содержать схемы встроенного самотестирования. Подобный подход позволяет повысить надежность цифровых систем и ускорить их разработку за счет использования готовых решений.

Анализ последних публикаций. В [1] рассмотрена архитектура FPGA различных производителей, описаны тенденции развития FPGA-технологий, рассмотрены методы и средства проектирования цифровых устройств на основе FPGA.

Результаты исследований [2, 3, 4] говорят о том, что отказы RAM составляют до 70% общего числа отказов цифровых систем. Таким образом, RAM является одним из наиболее уязвимых элементов.

В [4, 5] предложены модели и методы синтеза FPGA-структур для ответственных приложений.

В [4] выполнен анализ методов организации самотестирования RAM, где в качестве перспективного авторы рассматривают маршевый неразрушающий тест MARCH C-.

В [4] также показано, что построение систем со встроенными схемами самотестирования позволяет периодически выполнять тестирование на внутренней частоте без применения внешнего оборудования. При этом большинство устройств со встроенной аппаратурой самотестирования (ВАСТ) реализуют тесты сложности О(N) (N-емкость запоминающего устройства), называемые маршевыми тестами. Достоинствами маршевых тестов являются относительно высокие скорость выполнения и покрывающая способность, а так же простота реализации ВАСТ. В большинстве случаев используют методы, основанные на преобра-

зовании классических маршевых тестов к неразрушающему виду.

**Целью статьи** является повышение эффективности проектирования цифровых систем на основе FPGA, связанных с безопасностью, путем разработки и исследования HDL-модели резервируемой памяти RAM со встроенной схемой неразрушающих тестов.

**Основные материалы исследования.** Память RAM в FPGA, как правило, реализуется в виде блоков двухпортовой памяти типа SRAM (например, 6-я серия FPGA фирмы Xilinx содержит блоки RAM 18 kb).

В [5] перечислены наиболее часто встречающиеся неисправности RAM, построенной по технологии SRAM (табл. 1).

Таблица 1 — наиболее распространенные неисправности SRAM

| Отказы SRAM                                                       | Модель<br>отказа |  |  |

|-------------------------------------------------------------------|------------------|--|--|

| Замыкания и обрывы в ячейках памяти                               | SAF, SCF         |  |  |

| Замыкания и обрывы в декодере адреса                              | AF               |  |  |

| Ошибка момента доступа к декодеру адреса                          | Functional Fault |  |  |

| Паразитные емкостные связи между ячейками                         | CF               |  |  |

| Залипание транзистора в открытом состоянии                        | SOF              |  |  |

| Отказы в структуре между ячей-ками                                | PSF              |  |  |

| Разомкнутый подтянутый транзистор (влечет за собой потерю данных) | DRF              |  |  |

В табл. 2 [5] перечислены известные модели отказов RAM и наименования тестов, которые способны их выявлять.

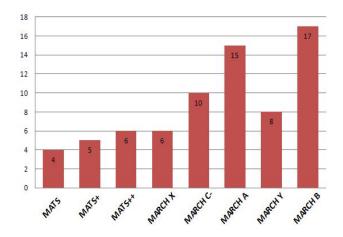

Данные, приведенные в [4, 5] позволяют построить гисторгамму сложности различных видов неразрушающих тестов (рис. 1).

Таблица 2 – Способность к выявлению отказов для алгоритмов неразрушающих маршевых тестов

| Algorithm | SAF | ADF  | TF  | CF in (inversion) | CF 1d<br>(idempote<br>nt) | CF dyn<br>(dynamic) | SCF |

|-----------|-----|------|-----|-------------------|---------------------------|---------------------|-----|

| MATS      | All | Some |     |                   |                           |                     |     |

| MATS+     | All | All  |     |                   |                           |                     |     |

| MATS++    | All | All  | All |                   |                           |                     |     |

| MARCH X   | All | All  | All | All               |                           |                     |     |

| MARCH C-  | All | All  | All | All               | All                       | All                 | All |

| MARCH A   | All | All  | All | All               |                           |                     |     |

| MARCH Y   | All | All  | All | All               |                           |                     |     |

| MARCH B   | All | All  | All | All               |                           |                     |     |

Рисунок 1 — Зависимость сложности маршевого теста от его вида

Перед началом синтеза модели необходимо сформулировать требования и определить подходы к реализации.

HDL-модель должна:

- описывать двухканальную архитектуру цифрового устройства хранения данных, которое реализовано в виде двухпортовой RAM со встроенной схемой генерации неразрушающих тестов;

- учитывать разнесение каналов RAM на разные кристаллы для обеспечения независимости отказов;

- обеспечивать взаимный контроль результатов тестирования между каналами;

- в случае обнаружения сбоя или отказа в собственном или соседнем канале выдавать сообщение об ошибке для перевода канала в необратимое защитное состояние.

Выполнение указанных требований может быть достигнуто за счет:

- использования неразрушающего маршевого теста MARCH C-, обеспечивающего наибольшее покрытие отказов среди всех рассмотренных вариантов и

сравнительно невысокую сложность;

- обеспечения взаимного контроля формирования тестовых последовательностей и откликов путем подсчета контрольных сумм входных и выходных сигналов RAM в процессе тестирования с последующим обменом контрольными суммами между каналами.

Тест MARCH C- имеет симметричный алгоритм и записывается следующей формулой [4]:

$$\uparrow (r_{\overline{a}}); \uparrow (r_{\overline{a}}, w_{\overline{a}}); \uparrow (r_{\overline{a}}, w_{\overline{a}}); \downarrow (r_{\overline{a}}, w$$

rде r — операция чтения; w — операция записи.

Первая и последняя операции в выражении (1.1) выполняются исключительно для того, чтобы можно было сравнить результаты тестирования. Для обеспечения функциональной безопасности устройства, описываемого синтезируемой моделью, необходимо обеспечить сверку результатов тестирования первого и второго каналов. Для этого достаточно выполнить межканальный обмен контрольными суммами (или другими видами сигнатур), которые вычисляются в процессе тестирования и фиксируют входные и выходные сигналы тестируемого компонента. В связи с этим выражение (1.1) упростится и примет следующий вид:

$$\uparrow (r_a, w_{\overline{a}}); \uparrow (r_{\overline{a}}, w_{\overline{a}}) \downarrow (r_a, w_{\overline{a}}); \downarrow (r_{\overline{a}}, w_{\overline{a}}). \tag{1.2}$$

Таким образом, обмениваясь контрольными суммами между двумя каналами, мы имеем возможность проверять не только успешность прохождения теста в SRAM, но и сам аппарат тестирования, включая линии связи, модуль формирования тестовых воздействий и модуль подсчета контрольных сумм.

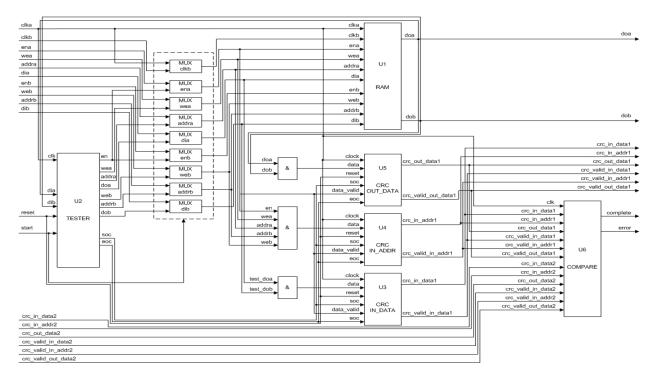

Структурная схема HDL-модели, соответствующей сформулированным требованиям и реализующей алгоритм (1.2), приведена на рис. 2.

Данная HDL модель может работать в двух режимах: 1-й — нормальная работа с памятью и 2-й — режим тестирования памяти. При работе в режиме тестирования тестовые воздействия на RAM подаются через нижние входы мультиплексоров, таким образом, RAM в момент тестирования отключена от рабочей схемы.

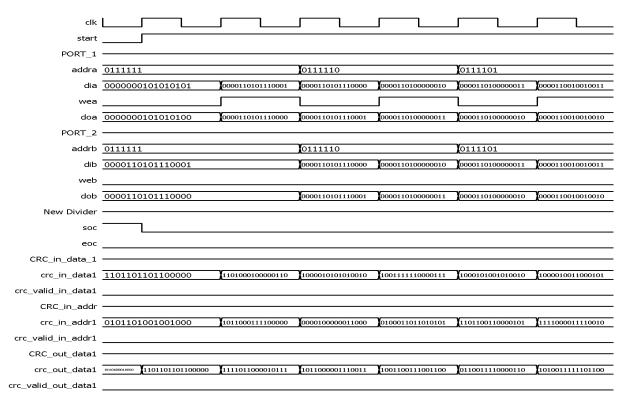

Реализованная HDL-модель имеет настройки ширины и глубины шины данных в пределах 18 Кb. Блок U1 (RAM) представляет собой стандартную для семейства ПЛИС Xilinx 6-й серии двухпортовую память. Блок U2 (TESTER) формирует воздействия на U1 в соответствии с алгоритмом (1.2). Все входные и выходные данные с RAM проходят через блоки конкатенации и попадают на блоки подсчета контрольной суммы CRC-8-CIIT. Поскольку память двухпортовая, а алгоритм тестирования симметричный, то первая часть алгоритма будет проходить по первому порту, а вторая по второму. Процесс прохождения теста в первом канале показан на временной диаграмме (см. рис. 3).

Рисунок 2 — HDL-модель RAM с самотестированием

Как видно из диаграммы, при формировании на адресной шине addra комбинации "0111110" осуществляется считывание содержимого ячейки памяти "0000110100000010" (шина dia). Одновременно этот же сигнал с инверсным нулевым битом попадает на вход doa. Запись осуществляется по сигналу wea = '1' на следующем такте после его формирования. Аналогичный алгоритм проведения теста реализуется для второго порта памяти.

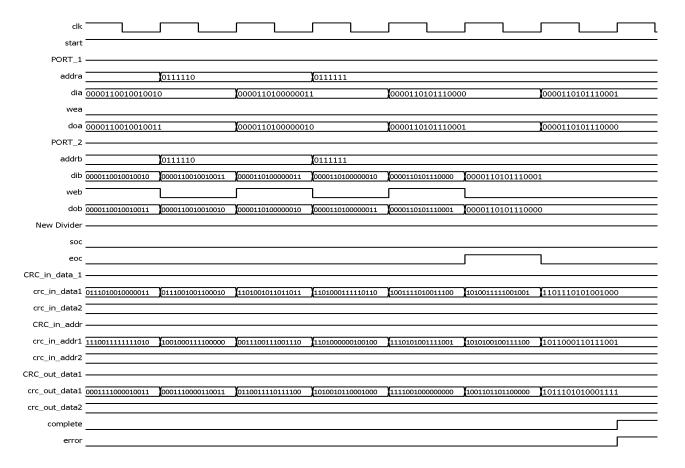

Межканальный обмен контрольными суммами и сравнение результатов тестирования иллюстрируются диаграммой на рис. 4. После реализации алгоритма тестирования все данные, записанные в ячейки RAM, вновь принимают исходные значения. В частности, в ячейке памяти с адресом addra = "0111110" находятся данные dia = "0000110100000010", что соответствует содержимому ячейки на момент начала тестирования.

Рисунок 3 — Временная диаграмма тестирования RAM по первому порту

Рисунок 4 — Временная диаграмма результатов тестирования RAM

Блок U6 (Compare) обеспечивает сравнение контрольных сумм первого и второго каналов и формирует сигнал ошибки error = '1' в случае их неравенства.

**Выводы.** Реализованная HDL-модель памяти RAM со встроенной схемой самотестирования соответствует сформулированным требованиям и может быть использована для построения библиотечных компонентов памяти при проектировании цифровых систем, связанных с безопасностью.

Реализованный метод тестирования гарантирует выявление отказов, описываемых моделями, приведенными в [5], а также отказов схем генерации тестовых воздействий за счет взаимного контроля формирования тестовых последовательностей и откликов путем подсчета контрольных сумм входных и выходных сигналов RAM в процессе тестирования.

#### Список использованных источников

- 1 Сергиенко А. М. VHDL для проектирования вычислительных устройств / А. М. Сергиенко. Киев: ЧП "Корнейчук", 2003. 208 с.

- 2 Prince B. High-performance memories: new architecture DRAM's and SRAM's, evolution and function / B. Prince. Gr.Britain: John Wiley & Sons, 1996.

- 3 Goor A. J. Testing Semiconductor Memories, Theory and Practice / A. J. Goor. Gr.Britain: John Wiley & Sons, 1991.

- 4 Ярмолик В. Н. Симметричное неразрушающее тестирование ОЗУ / А. П. Занкович, В. Н. Ярмолик // Доклады белорусского государственного университе-

та информатики и радиоэлектроники. — 2005.

5 Michael L. Essentials of electronic testing for digital, memory and mixed-signal VLSI circuits / L. Michael, D. Vishwani. — Kluwer: Academic Publishers, 2002. — 671 c.

## Анотація

## HDL-МОДЕЛЬ ПАМ'ЯТІ RAM З ВБУДОВАНОЮ СХЕМОЮ ГЕНЕРАЦІЇ НЕРУЙНУЮЧИХ ТЕСТІВ

Малиновський М. Л., Алєнін Д. О., Барсов В. І., Сидоренко А. В.

Запропоновано HDL-модель пам'яті RAM з вбудованою схемою генерації неруйнуючих тестів, котра дозволяє підвищити ефективність проектування цифрових систем для відповідальних застосувань.

### **Abstract**

## HDL-MODEL OF MEMORY RAM WITH NONDESTRUCTIVE TEST GENERATOR INSIDE

M. Malinovsky, D. Alenin, V. Barsov, A. Sidorenko

We propose the HDL-model of memory RAM with an integrated scheme of generation of nondestructive testing, which improves the efficiency of designing digital systems for critical application.